1.VHDL Code for 4 bit comparator

2.VHDL code for d flip flop

3.VHDL code for 2 to 4 binary decoder

______________________________________________________________________________

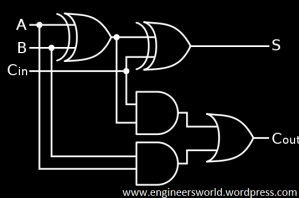

Here is the VHDL code for FULL ADDER:

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY fulladd IS

PORT ( Cin, x, y : IN STD_LOGIC ;

s, Cout : OUT STD_LOGIC ) ;

END fulladd ;

ARCHITECTURE beh OF fulladd IS

BEGIN

s <= x XOR y XOR Cin ;

Cout <= (x AND y) OR (Cin AND x) OR (Cin AND y) ;

END beh ;

Subscribe us for more such details directly to your mail,and write here for any of your queries and suggestions.

in behavioural modelling there are two BEGINS in syntax , one is for declarative part and another is for statement part. The one in declarative part consist of process , u havn't shown them here.

ReplyDeleteSYNTAX

begin

p1:process(A,B,Cin)

begin

S<=x XOR y XOR Cin;

............continued

very useful................

ReplyDeletecan we create an full adder with 2 proccesses? like this

DeleteP1: process (A, B)

begin

int1<= A xor B;

int2<= A and B;

end process;

P2: process (int1, int2, Cin)

begin

D <= int1 xor C;

int3 <= int1 and C;

E <= int2 or int3;

end process;

i need vhdl code for 16*16 booth multiplier.......plz send me

Deletehi you have started architecture and started with begin keyword so you need one end extra.

ReplyDeletebye

the [architecture _declarative_part ] is optional part ...so it can be written or left as per the requirement.

ReplyDeletedeclarative part and statement part defines strutural modelling not behavioral...

ReplyDeleteuseful program

ReplyDeletei need the vhdl code for (adders,counters,flipflops,fsm,multiplexers,demiltiplexers)plz send it to my mail id

ReplyDeletehi daniel , soon i will upload the same...!!!

ReplyDeletethanx

hi could you please email me the vhdl code for full adder and Decimal Arthmetic Unit Design.

ReplyDeletethank you

hadi_077@hotmail.com

HI for the Full Adder code what is the input and how do we declare what to A, B and Cin is?

ReplyDeleteCould you email me? tay_yiming@hotmail.com

could you please send testing of full adder circuit using vhdl coding

ReplyDeletedoes this code work in Active HDL software

ReplyDeletei need the vhdl code for modified carry select adder ..can u pls provide the code ....

ReplyDeleteI all the time used to study piece of writing in news papers but now as I am a user of web thus from now I am using net for posts, thanks to web.

ReplyDeleteRunning ISim simulation engine ...

ReplyDeleteThis is a Full version of ISE Simulator(ISim).

ERROR: Signal Unknown signal received

what does x,y,z mean in this program

ReplyDeletecould you send me code of 'dual 2 line to 4 line decoders/demultiplexers'.?

ReplyDeleteImplement the function given by the equation y =Σm(4,5,9,10,12,13)

ReplyDelete